1关于电源六级能效

近几年内,很多电源厂家或者电源工程师都在为了更新六级能效而忙碌,新规要求倒逼产品升级换代,是好事,也是挑战。 六级能效的标准是什么呢?到底怎么样做?

关于六级能效,两个要求: 一,待机功耗

二,平均效率

针对这两点,光选用哪家公司的新芯片是不够的,还有电源电路中很多细节设计也是非常重要的,下面咱们一起来分析分析。

首先,了解标准必不可少: 美国能效要求

2待机功耗设计攻略以美国能效要求为例,要求49W以下空载功耗为0.1W,大于49W空载功耗为0.21W;欧盟49W以下为75mW,大于49W为150mW。在设计电源时,相对于75mW的空载功耗,必须要精打细算到每个细节上。 下面一步步来分析:

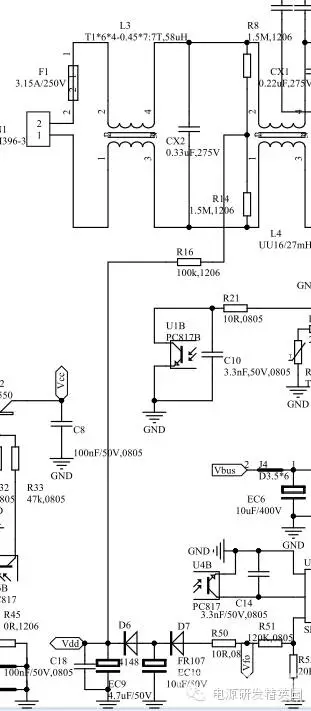

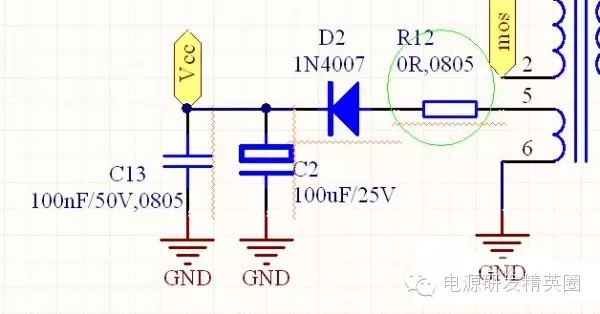

Vcc启动回路 首先,近几年有很多新出的IC大多具有HV启动关断功能,启动后关闭启动电阻回路,避免此回路损耗。当然,这属于IC原有功能,不在本问的重点中,这里一带过,同时后面的一些延伸也会用到此引脚,顺带一说。如下: 当你用的芯片没有启动关断功能的芯片该怎么?下面分享一个小技巧如下图,Vcc只能尽量大启动电阻,大的启动电阻又需要较快的启动时间时,可以这样做,Vcc两级DC接法,C16用于启动储能,C14用于辅助供电储能,使启动时较大R的情况下C能更快充到IC启动阈值: 放电

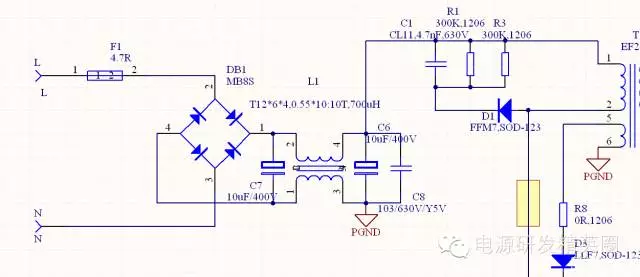

IEC60950要求1S内电压下降到37% IEC60065要求2S内电压下降到35V以下 X电容放电时间常数RC需小于1, 设X电容为0.33uF,Rx*Cx<1,那么Rx<3MΩ,由于电容量存在20%误差,那么此电阻选值留足裕量,那应在Rx*0.7内,约2MΩ。 电阻损耗, PR=U2/R,设ACmax=264V PR=2642/2M PR=34.8mW CoC要求49W以下75mW待机或DoE要求49W以下100mW待机,不管那个标准,这部份的损耗都显得巨大。需要符合安规要求,放电必须快,但损耗又大那该如何入手呢。像下面这种接法肯定是行不通的。 怎么办?下面分享一下技巧 不放放电电阻又过不了安规,可以选择使用更小的X电容,但X电容不放有时EMI不好整,得进一步想办法让这个R更灵活一点,如下: 技巧一、在断电后,利用IC的HV脚对Cx进行放电。 [url=]技巧二,在没有HV启动脚的情况下,将启动电阻接到X电容放电电阻中点,断电后,利用IC的Vcc脚帮助放电,可减小X电容两端电阻的放电功率:[/url] [url=]

[/url]

[/url] [url=]技巧三,把EMC元件后移动,AC端不放X电容:[/url] [url=]

[/url]

[/url] [url=]Vcc供电电路[/url] [url=]

[/url]

[/url] 1)、尽量选用芯片供电电压和电流小的芯片。 2)、 尽量小的Vcc限流电阻,减小损耗。 3)、变压器设计时在保证芯片能正常工作的情况下匝数尽量少不但能降低待机功耗还能提升工作时整机效率,最后实际测试后尽量优化。

[url=][/url] 环路采样电阻 较小的电压标测环流,如图流经R11、R16的静态电流。

图中两电阻75K+7.5K,回路静态电流约U/R=0.3mA, I2R约7.5mW。

如设为47K+4.7K,则U/R=0.49mA, I2R约12.5mW。

所以在环路允许的情况下,建议选取较大值。 假负载

一般为了稳定环路在输出预加一定的假负载,在目前6级能效来说,几乎不能接受,假设一个5V1A的电源预加1KR电阻假负载,实际消耗P=U2/R,实际上消耗25mW的功耗,已占COC待机要求的1/3。

所以要稳定,设整合适的环路才是正道。

待机功耗设计攻略小结 1,Vcc启动回路 对于传统芯片由于启动电流比较大,可选用启动电流尽量小的芯片,最好选用有启动后关断启动电阻通路的芯片。

2,X电容放电回路 安规标准里要求关断输入电源在很短时间内输入端口的电压要降到百分之三十多,所以这个要利用一定的技巧来放电: 利用芯片的高压启动脚放电 利用启动电阻放电 把X电容放到整流桥之后

3,IC Vcc供电回路 1)、尽量选用芯片供电电压和电流小的芯片。 2)、 尽量小的Vcc限流电阻,减小损耗。 3)、变压器设计时在保证芯片能正常工作的情况下匝数尽量少不但能降低待机功耗还能提升工作时整机效率,最后实际测试后尽量优化。

4,电压(电流)检测环路 选择环路检查电阻的时候,在环路稳定的前提下尽量用大的电阻来降低损耗。一定要确保环路稳定哦。

5,假负载 环路稳定的前提下尽量选大阻值的电阻

6,选取间歇式振荡的芯片,在电源待机时效果非常的明显。

7、线路中所有元件均存在消耗,所以,对各部份电路具体核算功耗,再尽可能把功耗降到最低。

2平均效率设计攻略

涉及效率,几乎包含了电源的整个系统设计,从整流到变压器转换,再到整流DC输出所有有电流过的地方都涉及损耗,包括EMI的抑制。要提升效率就是提升整个系统设计的合理性和平衡。不再大范围讲解,主要讲述一些重点和我们容易忽略的一些细节。 桥堆

桥堆的在电源工作时损耗是比较大的地方,桥堆二极管的压降(Vf值)有很大差异选取时要注意。

看看下面两个表,压降差了0.1V Pdiode=Vf*Iavg input curretn 常被忽略的参数,其实一直在侵食我们的效率。输出整流二极管 输出整流D5选用更低Vf的二极管,CCM下需要更快的Trr,如肖特基。

Vf直接影响损耗及发热

较低的Vf会有小的Pd=Vf*Iout

如下,同品牌在同等条件下参数对比:

MBRB20100CT Vf:0.95V

MBR20H100CT Vf:0.88V

损耗差Pd=(0.95-0.88)*Iout

当然实际使用电流下的Vf并不一定为上面标称值,但两者的差别对比,在设计效率上应尽量用更低Vf整流二极管。

变压器

对变压器的几点要求:

1,尽量低的漏感,可降低损耗,设漏感为Lkp

Plk=(1/2*Lkp*Ipk^2)*F

在确定的F情况下,较低的Ipk和Lkp可得到较低的漏感损耗

改善方法:

增加耦合面,用三明治或五明治绕线

副边较粗的线从Bobbin两端出线,不要横跨线包到Pin脚,减少后面绕组的间隙,降低漏感。

2,铜损、铁损

平衡两方损耗,监测两方面的温升,调整线匝及气隙,使温升平均尽量绕满绕线窗,最大利用变压器功率密度.。 然后变压器的磁芯方面要注意,选取横截面积比较大的磁芯可以减少绕组的圈数,这对于降低铜损是很有意义的。 合理的EMI

一般60W及以下产品设计合理的情况下,初级一个大感量共模,次级一个小共模可满足一般IT类同等的EMI要求

从效率和EMI考虑上,变压器线包内屏蔽建议用2个铜箔分隔三明治中的初次级,如再增加屏蔽效用不高

合理处理MOS及二极管上的高频噪声,一般串磁珠是较高效低成本的应用

初级大电解并瓷片电容,对噪声有很好滤除作用 PCB Layout 于效率上的影响,PCB上大的环路线路要短,线宽,尽量小的环流面积。

特别次级DC侧,电流要比初级大得多,线宽要控制好。35um 2mm宽1A电流走线(露铜上锡宽度减半),达不到的地方用露铜上锡加粗或在板面上加跳线增大电流。 针对六级能效,目前新IC推出很多特色功能来提升待机和能效,能满足我们应用的IC非常多,基本有几个特点:

待机方面

1,低启动电流,目前uA级的6Pin。或具HV独立启动的8Pin

2,轻载突发模式(间歇振荡式工作)

效率方面

1,频率反走

2,低压升频(变压器可用较少规格)

|